Dank Weiterentwicklungen in der Automobil- und Sensortechnik werden kommende Automobilgenerationen mit einer Vielzahl an verschiedenen Sensorsystemen ausgestattet sein, die eine große Menge an Sensordaten für Fahrerassistenzsysteme aufzeichnen. Diese Systeme nutzen diese Daten dann zur möglichst optimalen Wahrnehmung des Fahrzeugumfelds. Insbesondere optische Systeme basierend auf mehreren Kameras erzeugen dabei erhebliche Datenmengen. Bei steigenden Auflösungen werden leistungsfähige Steuergeräte und Rechnerarchitekturen notwendig, um die zwingend notwendige Echtzeitverarbeitung dieser Daten zu garantieren.

Da im Fahrzeug allerdings nur ein sehr begrenztes elektrisches Leistungsbudget zur Verfügung steht, scheiden stromhungrige Recheneinheiten wie Standardprozessoren oder aktuelle Grafikkarten als potentielle Plattformen aus. FPGAs dagegen bieten relativ hohe Rechenleistung bei moderatem Stromverbrauch und stellen damit eine potentielle Rechnerarchitektur für das Steuergerät der Zukunft dar.

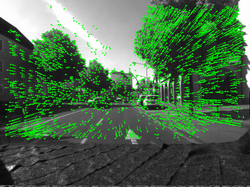

Daher befasst sich das IDA in Kooperation mit Volkswagen mit dem Entwurf und der Konzeption einer FPGA-basierten Rechenplattform für kamerabasierte Fahrerassistenzsystemen. Neben der Bereitstellung der Plattform sind die Entwicklung einer leistungsfähigen Programmierumgebung sowie die Implementierung von relevanten Algorithmen aus dem Bereich der Umfeldwahrnehmung weitere Kernziele des Projekts.

Im Rahmen des Projekts befasst sich das IDA mit zwei zentralen Aspekten:

Weitere Aspekte wie das Konzept der Plattform, die Kopplung mit anderen ECUs und Systemen, die Selektion und Implementierung von geeigneten Bildverarbeitungsalgorithmen oder die Einbindung von Fremdkomponenten werden in Kooperation mit Volkswagen bearbeitet. Außerdem existieren inhaltliche Überschneidungen mit dem DFG-geförderten Projekt Digital Chameleon, das sich mit der Konzeption eines automatisierten Entwurfsprozesses für die FlexWAFE-Architektur befasst.

Henning Sahlbach

Sean Whitty